本文简要分析说明嵌入式软件工程师需要了解的RISC-V的指令集内容.

指令集体系结构

指令集体系结构(ISA)是软硬件接口的一个定义,定义了软件操控计算机硬件的所有内容。主要包含:

- 所有指令及指令作用,格式。

- 指令操作数的类型和寻址空间。

- 寄存器数量,位数,编号,功能。

- 存储空间。

- CPU工作状态和切换。

- 存储保护方式。

- 中断/异常结构。

- 特殊硬件(例如timer)。

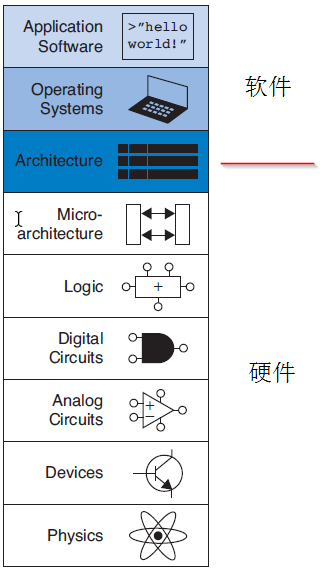

下面这副图是从Digital_Design_and_Computer_Architecture一书中摘录出来,从上到下的展示了计算机的层次结构:

其中Architecture这一层对应的就是ISA,作为嵌入式软件工程师,需要了解的就是从Architecture往上的内容,如果要对程序做到极致的优化需要部分了解微结构(Micro-architecture)。

RISC-V指令集

逻辑电路提供基本的运算和时序模块,微结构按照一定的设计将这些模块组合起来提供给软件,指令就是软件到这些硬件的桥梁。而指令集就是一种CPU支持所有指令的集合。RISC-V采用模块化的指令集,由基础指令集模块提供基础的CPU功能,由扩展指令集模块提供不同的高级功能,这样既避免了增量化指令集的庞大又满足了多样性. 一颗RISC-V芯片提供一个基础的RISC-V指令集和0到多个扩展指令集的支持。

RISC-V基础指令集

RISC-V的核心(core)包含一个基础指令集(Base Instruction Set),基础指令集有如下几种:

- RV32I: 32位整型指令集,指令长度32bit,32个32bit通用寄存器

- RV32E:基于RV32I简化,用于嵌入式CPU,只有16个通用寄存器,其它和RV32I一样

- RV64I: 基于RV32I变化,支持64bit地址空间,寄存器变为64bit宽,对RV32I指令格式进行了部分修改。

- RV128I:基于RV64I变化,支持128bit地址空间,寄存器变位128bit宽.

RV32E,RV64I,RV128I相对于RV32I的变化非常小,因此嵌入式软件工程师入门RISC-V,只需要先掌握RV32I指令集即可。

RISC-V扩展指令集

在RISC-V的协处理器(accelerator)提供的功能由扩展指令集(Extension Instruction Set)描述。下面列出一些主要的扩展指令集:

- M: 乘法扩展,提供乘法和除法指令

- A: 原子操作扩展

- F: 单精度浮点扩展

- D:双精度浮点扩展

- Q: 四精度浮点扩展

- L: 十进制浮点扩展

- C: 压缩指令扩展, 将指令压缩位16bit

- B: 位操作扩展

- J: 动态翻译扩展,例如java的动态检查和垃圾回收可以得到ISA的硬件支持

- P: 单指令多数据流扩展(SIMD)

- V: 向量操作扩展

可能是出于没有CSR的计算机也可以独立运行的考虑,在最新的RISC-V Spec中已经将操作CSRC寄存器的指令独立为”Zicsr”扩展,让基础指令集更为精简。单出于习惯,后续的文章中还是将CSR的指令放入到RV32I中一起介绍。

当你拿到一颗RISC-V的芯片时,看到Spec中写的RV32I/M/C/F,那么就可以知道CPU支持RV32I基础指令集,乘法扩展,压缩指令扩展和单精度浮点扩展。

总结

通过对RISC-V指令集的了解,我们可以知道嵌入式软件工程师要入门RISC-V,可以先从RV32I着手,而其它的都是扩展和变形,可以用时再看。

参考

https://cseweb.ucsd.edu/classes/wi20/cse140-b/Digital_Design_and_Computer_Architecture_2nd_edition.pdf

http://crva.io/documents/RISC-V-Reader-Chinese-v2p1.pdf

https://github.com/riscv/riscv-isa-manual/releases/download/Ratified-IMAFDQC/riscv-spec-20191213.pdf